Tewksbury, MA – May 25, 2021 - Avery Design Systems Inc., an innovator in functional verification productivity solutions, today announced availability of major updates to the company’s flagship PCI Express® (PCIe®) 6.0 and PIPE 6.0 VIP solution. Avery unveiled the solution at the PCI-Sig DevCon event this week.

The solution supports the latest features and capabilities in the high-speed interconnect protocol, including a doubling of data rates compared to PCIe 5.0, to 64 GT/s speeds, its move to PAM4 encoding and FLIT mode, the introduction of low latency FEC, and backwards compatibility with all previous specification versions.

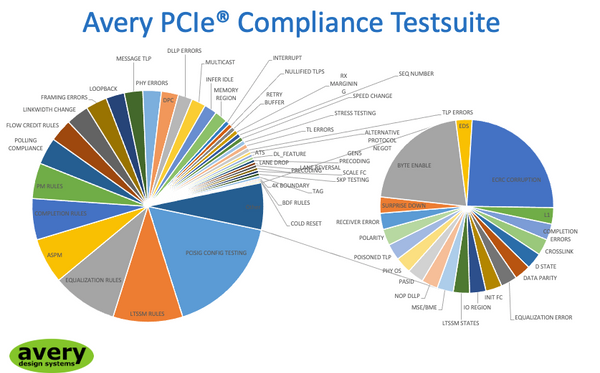

The Avery PCIe 6.0 VIP solution enables advanced debug and compliance checking, and allows designers to run pre-silicon compliance testsuites. The updated Avery VIP supports co-simulation using a QEMU, speeding development time with early HW-SW integration with host OS and embedded software.

“Avery is a leader in PCIe and CXL VIP and we’re working with several PCIe 6.0 early adopters already as as the industry targets PCIe 6.0 and CXL 2.0 for an entirely new class of memory systems, SSDs, networking, GPUs, and many other devices, it creates heightened verification challenges given still no mainstream commercial platforms support the latest standard,” said Chris Browy, vice president of sales/marketing at Avery. “Our customers can be confident in developing their new products knowing our SystemVerilog/UVM VIP solution - including models, protocol checking, compliance testsuites, and Virtual Host QEMU co-simulation - will be able to tackle these new PCIe 6.0 design and verification challenges. Plus our ecosystem partnership efforts with several prominent controller and PHY IP and test vendors creates a best in class total IP solution.”

Avery PCIe VIP highlights

• UVM agents for Root Complex, Endpoint, SR-IOV Endpoint, Retimer, Switch, PHY including PIPE and serial interfaces

• Advanced capabilities including full BIOS enumeration and port bifurcation and advanced error injection support

• PCI-SIG® compliance checkers and coverage isolates bugs faster

• Protocol-aware analyzer tracker eases debug

• PCI-SIG based and Avery-built compliance testsuites

• Random DUT configuration and runtime behaviors improves interop and boundary case testing

• Complimentary VIPs portfolio includes CXL, CCIX, NVMe, CXS, CPI, SFI, LPIF for block through SoC integration

Avery Design Systems

Founded in 1999, Avery Design Systems, Inc. enables system and SOC design teams to achieve dramatic functional verification productivity improvements through the use of formal analysis applications for gate-level X-pessimism verification and real X root cause and sequential back tracing; and robust core-through-chip-level Verification IP for PCI Express, CXL, CCIX, Gen-Z, USB, AMBA, UFS, MIPI CSI/DSI, I3C, DDR/LPDDR, HBM, ONFI/Toggle/NOR, NVM Express, SATA, AHCI, SAS, eMMC, SD/SDIO, CAN FD, and FlexRay standards. The company has established numerous Avery Design VIP partner program affiliations with leading IP suppliers.

PCI Express and PCIe® are trademarks of PCI-SIG