Tewksbury, MA, February 28, 2023 — Avery Design Systems, a leader in functional verification solutions, today announced a new validation suite supporting the Compute Express Link™ (CXL™) open industry-standard interconnect. It enables rapid and thorough system interoperability, validation and performance benchmarking of systems targeting the full range of versions of the CXL standard, including 1.1, 2.0 and 3.0. The comprehensive validation suite covers both pre-silicon virtual and post-silicon system platforms and extends Avery’s leadership in enabling designs incorporating industry-standard protocols for high-speed interconnect.

The company is currently working with several lead partners and industry validation groups to further qualify the suite.

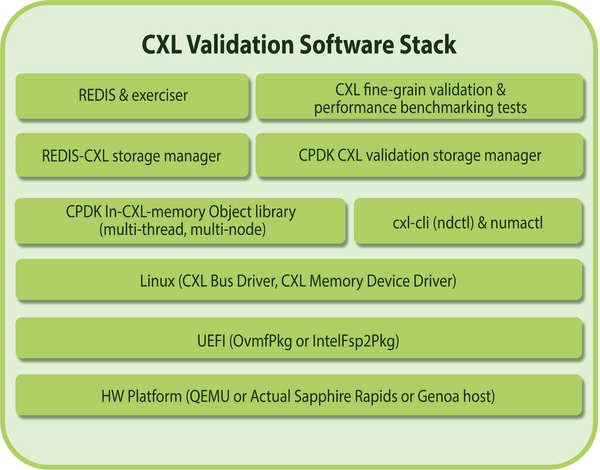

The CXL validation suite, available now, focuses on supporting 4 main areas:

- Bring-up tests of CXLTM devices using OS In-band Management Stack components including ndctl and sysfs to access and configure CXL devices in various system topologies for memory expander and pooling contexts;

- Use of CXL compliance verifier (CXLCV) to utilize the Compliance Working Group tools in pre-silicon environment;

- CXL Performance Development Kit (CPDK) supports performance benchmarking and validation framework for fine-grained verification performance and latency measurement using set of pre-defined and customizable high memory access stress workloads;

- Extending select industry distributed, in-memory enterprise software for fine-grained performance measurement.

“Sharing the same validation suite across pre- and post-silicon enables hardware and software development teams to start system integration and validation extremely early in the project while still working with Verilog RTL simulation and emulation. This helps accelerate time to market, reduce risk, and improve confidence in deployment,” said Chris Browy, VP Sales and Marketing of Avery Design Systems.

Avery provides a robust suite of CXL VIP to support the verification of the open industry standard’s interconnect offering of high-bandwidth, low-latency connectivity between host processor and devices such as accelerators, memory buffers, and smart I/O devices. VIP is available for designs using current versions of the standard as well as design targeting more advanced versions, including 3.0 which doubles the bandwidth and adds new features, all of which are supported in the Avery VIP

In addition, Avery’s QEMU open software virtual machine emulator environment allows software engineers to natively develop and build custom firmware, drivers, and applications and run them unaltered as part of a comprehensive system-level validation process using the actual SoC RTL hardware design. In a complementary manner, hardware engineers can evaluate how the SoC performs through executing UEFI and OS boot and custom driver initialization sequences in addition to running real application workloads and utilize the CXL protocol aware debugging features of the VIP to effectively investigate any hardware related issues.